اینٹی ایلائزنگ فلٹرز اور وولٹیج سٹیبلائزرز

ہموار کرنے والے فلٹرز درست وولٹیج کی لہر کو کم کرنے کے لیے بنائے گئے ہیں۔ ریپل اسموتھنگ کا اندازہ ہموار کرنے والے عنصر q سے کیا جاتا ہے۔

ہموار کرنے والے فلٹرز درست وولٹیج کی لہر کو کم کرنے کے لیے بنائے گئے ہیں۔ ریپل اسموتھنگ کا اندازہ ہموار کرنے والے عنصر q سے کیا جاتا ہے۔

ہموار کرنے والے فلٹرز کے اہم عناصر کیپسیٹرز ہیں، انڈکٹرز اور ٹرانجسٹر جن کی مزاحمت براہ راست اور متبادل کرنٹ کے لیے مختلف ہے۔

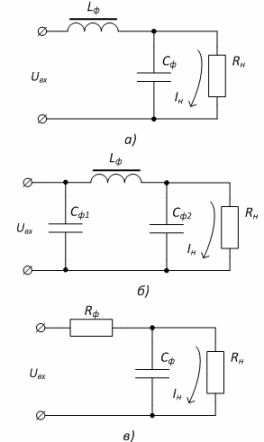

فلٹر عنصر کی قسم پر منحصر ہے، capacitive، inductive اور الیکٹرانک فلٹرز کے درمیان فرق کیا جاتا ہے۔ فلٹرنگ لنکس کی تعداد کے مطابق، فلٹرز کو سنگل لنک اور ملٹی لنک میں تقسیم کیا گیا ہے۔

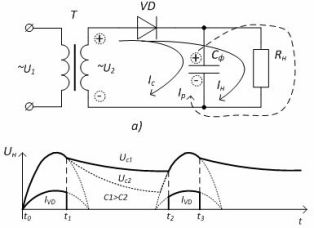

ایک کیپسیٹو فلٹر ایک کپیسیٹر ہے جس کی بڑی صلاحیت ہے جو لوڈ ریزسٹر Rn کے متوازی طور پر جڑی ہوئی ہے۔ ایک کپیسیٹر میں اعلی DC مزاحمت اور کم AC مزاحمت ہوتی ہے۔ آئیے نصف لہر ریکٹیفائر سرکٹ (تصویر 1، اے) کی مثال پر فلٹر کے آپریشن پر غور کریں۔

شکل 1-کیپسیٹو فلٹر کے ساتھ سنگل فیز ہاف ویو ریکٹیفائر: a) سرکٹ ب) آپریشن کے ٹائمنگ ڈایاگرام

جب ایک مثبت نصف لہر وقت کے وقفے میں بہتی ہے t0 — t1 (تصویر 2.63, b)، لوڈ کرنٹ (ڈائیڈ کرنٹ) اور کپیسیٹر چارج کرنٹ بہاؤ۔کپیسیٹر کو چارج کیا جاتا ہے اور وقت t1 پر کپیسیٹر میں وولٹیج سیکنڈری وائنڈنگ کے وولٹیج ڈراپ سے زیادہ ہو جاتا ہے — ڈایڈڈ بند ہو جاتا ہے اور وقت کے وقفے میں t1 — t2 لوڈ میں کرنٹ کیپسیٹر کے خارج ہونے سے فراہم کیا جاتا ہے۔ چے لوڈ میں کرنٹ مسلسل بہتا رہتا ہے، جو رییکٹیفائیڈ وولٹیج کی لہر کو نمایاں طور پر کم کرتا ہے۔

Capacitor Cf کی گنجائش جتنی زیادہ ہوگی، حوصلہ افزائی اتنی ہی کم ہوگی۔ اس کا تعین کیپسیٹر کے خارج ہونے والے وقت سے ہوتا ہے — خارج ہونے کا وقت مستقل τ = СfRн۔ τ> 10 پر، سموٹنگ گتانک کا تعین فارمولہ q = 2π fc m Cf Rn سے ہوتا ہے، جہاں fc نیٹ ورک کی فریکوئنسی ہے، m اصلاح شدہ وولٹیج کے نصف ادوار کی تعداد ہے۔

کم لوڈ پاورز پر اعلی مزاحمتی RH لوڈ ریزسٹر کے ساتھ capacitive فلٹر استعمال کرنے کی سفارش کی جاتی ہے۔

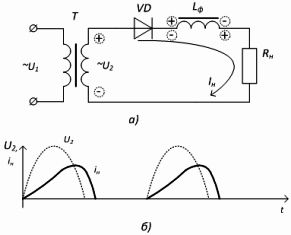

دلکش فلٹر (چوک) Rn کے ساتھ سیریز میں جڑا ہوا ہے (تصویر 3، اے)۔ انڈکٹنس میں کم ڈی سی مزاحمت اور اعلی AC مزاحمت ہے۔ ریپل سموتھنگ سیلف انڈکشن کے رجحان پر مبنی ہے، جو شروع میں کرنٹ کو بڑھنے سے روکتا ہے، اور پھر اس کی کمی کے ساتھ اس کی حمایت کرتا ہے (تصویر 2، بی)۔

شکل 2- سنگل فیز ہاف ویو ریکٹیفائر انڈکٹو فلٹر کے ساتھ: ا) سرکٹ، ب) آپریشن کے ٹائمنگ ڈایاگرام

انڈکٹیو فلٹرز درمیانے اور اعلیٰ طاقت کے ریکٹیفائرز میں استعمال ہوتے ہیں، یعنی بڑے لوڈ کرنٹ کے ساتھ کام کرنے والے ریکٹیفائر میں۔

ہموار گتانک کا تعین فارمولے سے کیا جاتا ہے: q = 2π fs m Lf / Rn

کیپسیٹو اور انڈکٹو فلٹر کا آپریشن اس حقیقت پر مبنی ہے کہ نیٹ ورک کے ذریعے استعمال ہونے والے کرنٹ کے بہاؤ کے دوران، کیپسیٹر اور انڈکٹر توانائی کو ذخیرہ کرتے ہیں، اور جب نیٹ ورک سے کوئی کرنٹ نہیں ہوتا ہے، یا اس میں کمی آتی ہے، عناصر فراہم کرتے ہیں۔ ذخیرہ شدہ توانائی کا بند ہونا، لوڈ میں کرنٹ (وولٹیج ) کو برقرار رکھنا۔

ملٹی جنکشن فلٹرز کیپسیٹرز اور انڈکٹرز دونوں کی ہموار خصوصیات کا استعمال کرتے ہیں۔ کم طاقت والے ریکٹیفائرز میں، جہاں لوڈ ریزسٹر کی مزاحمت کئی kOhm ہوتی ہے، چوک Lf کی بجائے، ریزسٹر Rf شامل ہوتا ہے، جو فلٹر کے بڑے پیمانے اور طول و عرض کو نمایاں طور پر کم کرتا ہے۔

شکل 3 LC اور RC سیڑھی کے فلٹرز کی اقسام کو دکھاتا ہے۔

شکل 3-ملٹی جنکشن فلٹرز: a) L-shaped LC، b) U-shaped LC، c) RC-فلٹر

اسٹیبلائزرز کو مینز وولٹیج میں اتار چڑھاو اور لوڈ کے ذریعے استعمال ہونے والے کرنٹ میں تبدیلی کے دوران بوجھ کے مستقل وولٹیج (کرنٹ) کو مستحکم کرنے کے لیے ڈیزائن کیا گیا ہے۔

اسٹیبلائزرز کو وولٹیج اور کرنٹ اسٹیبلائزرز کے ساتھ ساتھ پیرامیٹرک اور معاوضہ والے میں تقسیم کیا گیا ہے۔ آؤٹ پٹ وولٹیج کے استحکام کا اندازہ اسٹیبلائزیشن فیکٹر Kst سے کیا جاتا ہے۔

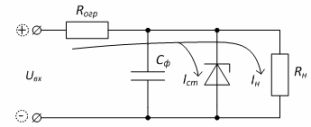

پیرامیٹرک سٹیبلائزر غیر لکیری خصوصیت والے عنصر کے استعمال پر مبنی ہے - ایک سیمی کنڈکٹر زینر ڈائیوڈ۔ ڈیوائس کے ذریعے ریورس کرنٹ میں نمایاں تبدیلی کے ساتھ زینر ڈائیوڈ کا وولٹیج تقریباً مستقل ہے۔

پیرامیٹرک سٹیبلائزر سرکٹ کو شکل 4 میں دکھایا گیا ہے۔ ان پٹ وولٹیج UBX کو محدود کرنے والے ریزسٹر Rlim اور متوازی منسلک zener diode VD اور لوڈ ریزسٹر Rn کے درمیان تقسیم کیا گیا ہے۔

شکل 4 — پیرامیٹرک سٹیبلائزر

جیسے جیسے ان پٹ وولٹیج بڑھے گا، زینر ڈائیوڈ کے ذریعے کرنٹ بڑھے گا، جس کا مطلب ہے کہ محدود کرنے والے ریزسٹر کے ذریعے کرنٹ بڑھے گا اور اس کے پار ایک بڑا وولٹیج گرے گا، اور لوڈ وولٹیج میں کوئی تبدیلی نہیں ہوگی۔

پیرامیٹرک اسٹیبلائزر میں 20-50 کے آرڈر کا Kst ہے۔ اس قسم کے اسٹیبلائزرز کے نقصانات کم اسٹیبلائزیشن کرنٹ اور کم کارکردگی ہیں۔

پیرامیٹرک اسٹیبلائزرز کو معاون وولٹیج کے ذرائع کے طور پر استعمال کیا جاتا ہے، ساتھ ہی جب لوڈ کرنٹ چھوٹا ہوتا ہے — سینکڑوں ملی ایمپس سے زیادہ نہیں۔

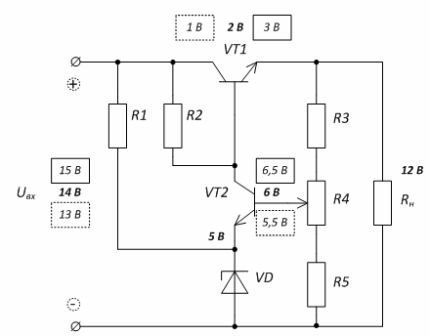

ایک معاوضہ دینے والا سٹیبلائزر ٹرانجسٹر کی متغیر مزاحمت کو محدود ریزسٹر کے طور پر استعمال کرتا ہے۔ جیسے جیسے ان پٹ وولٹیج میں اضافہ ہوتا ہے، ٹرانزسٹر کی مزاحمت بھی بڑھ جاتی ہے، اسی طرح، جیسے جیسے وولٹیج کم ہوتا ہے، مزاحمت کم ہوتی جاتی ہے۔ اس صورت میں، لوڈ میں وولٹیج میں کوئی تبدیلی نہیں ہے.

ٹرانزسٹرز کا سٹیبلائزر سرکٹ شکل 5 میں دکھایا گیا ہے۔ آؤٹ پٹ وولٹیج URn کو ریگولیٹ کرنے کا اصول ریگولیٹنگ ٹرانزسٹر VT1 کی چالکتا میں تبدیلی پر مبنی ہے۔

شکل 5 — معاوضہ وولٹیج ریگولیٹر کا منصوبہ

ٹرانجسٹر VT2 پر ایک وولٹیج موازنہ سرکٹ اور ایک DC یمپلیفائر جمع ہیں۔ پیمائش کرنے والا سرکٹ R3, R4, R5 اس کے بیس سرکٹ میں شامل ہے، اور حوالہ وولٹیج کا ذریعہ R1VD ایمیٹر سرکٹ میں شامل ہے۔

مثال کے طور پر، جیسے جیسے ان پٹ وولٹیج بڑھے گا، آؤٹ پٹ بھی بڑھے گا، جو ٹرانزسٹر VT2 کی بنیاد پر وولٹیج میں اضافے کا باعث بنے گا، جبکہ اسی وقت Emitter VT2 کی صلاحیت بھی وہی رہے گی۔یہ بیس کرنٹ میں اضافے کا باعث بنے گا، اور اس وجہ سے ٹرانجسٹر VT2 کا کلیکٹر کرنٹ — ٹرانزسٹر VT1 کی بنیادی صلاحیت کم ہو جائے گی، ٹرانزسٹر بند ہو جائے گا اور اس پر وولٹیج کا بڑا ڈراپ ہو گا، اور آؤٹ پٹ وولٹیج کم ہو جائے گا۔ کوئی تبدیلی نہیں رہے.

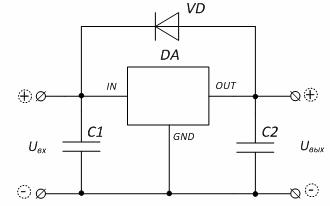

آج، سٹیبلائزر مربوط سرکٹس کی شکل میں تیار کیے جاتے ہیں۔ انٹیگریٹڈ سٹیبلائزر کو آن کرنے کی ایک عام اسکیم تصویر 6 میں دکھائی گئی ہے۔

شکل 6 — بلٹ میں وولٹیج سٹیبلائزر کو آن کرنے کے لیے مخصوص اسکیمیٹک

سٹیبلائزر مائیکرو سرکٹ کے آؤٹ پٹس کا عہدہ: «IN» — ان پٹ، «OUT» — آؤٹ پٹ، «GND» — عام (کیس)۔ اگر سٹیبلائزر سایڈست ہے، تو وہاں ایک آؤٹ پٹ ہے «ADJ» — ایڈجسٹمنٹ.

سٹیبلائزر کا انتخاب آؤٹ پٹ وولٹیج کی قدر، زیادہ سے زیادہ لوڈ کرنٹ اور ان پٹ وولٹیج کے تغیر کی حد پر مبنی ہے۔